News BoT

RSS Feed

Joined: 11 May 2006

Posts: 32637

|

Posted: Thu Feb 04, 2016 5:00 pm Post subject: ARM Announces New 28nm POP IP For UMC Foundry Posted: Thu Feb 04, 2016 5:00 pm Post subject: ARM Announces New 28nm POP IP For UMC Foundry |

|

|

<p align="center"> </p><p><p>Today ARM announces a new POP IP offering directed at UMC's new 28HPC<sup>U </sup><span style="color: rgb(68, 68, 68); line-height: 21px;">manufacturing process. To date we haven't had the opportunity to properly explain what ARM's POP IP actually is and how it enables vendors to achieve better implementation of ARM's IP offerings. While for today's pipeline announcement we'll be just explaining the basics, we're looking forward to a more in-depth article in the following months as to how vendors take various IPs through the different stages of development. </span></p> </p><p><p>Today ARM announces a new POP IP offering directed at UMC's new 28HPC<sup>U </sup><span style="color: rgb(68, 68, 68); line-height: 21px;">manufacturing process. To date we haven't had the opportunity to properly explain what ARM's POP IP actually is and how it enables vendors to achieve better implementation of ARM's IP offerings. While for today's pipeline announcement we'll be just explaining the basics, we're looking forward to a more in-depth article in the following months as to how vendors take various IPs through the different stages of development. </span></p>

<p><span style="color: rgb(68, 68, 68); line-height: 21px;">When we talk about a vendor licensing an ARM IP (CPU for example), this generally means that they are taking the RTL (Register Transfer Level) design of an IP. The RTL is just a logical representation of the functioning of a block, and to get to from this form to one that can be implemented into actual silicon requires different development phases which is generally referred to as the physical implementation part of semiconductor development. </span></p>

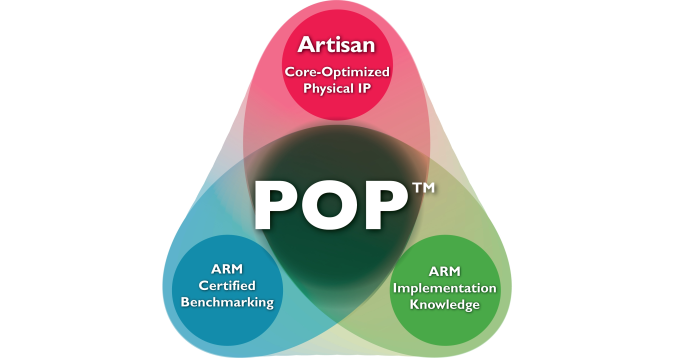

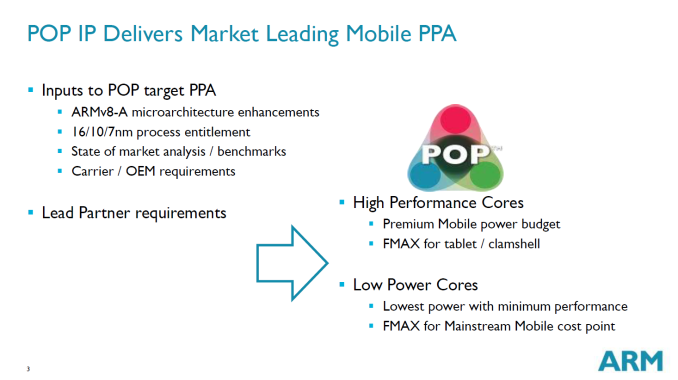

<p><span style="color: rgb(68, 68, 68); line-height: 21px;">It's here where ARM's POP IP (Which by the way not an acronym) comes into play: Roughly speaking, POP IP is a set of tools and resources that are created by ARM to accelerate and facilitate the implementation part of SoC development. This includes standard cell libraries, memory compilers, timing benchmarks, process optimized design changes and in general implementation knowledge that ARM is able to amass during the IP block development phase.</span></p>

<p style="text-align: center;">  </p> </p>

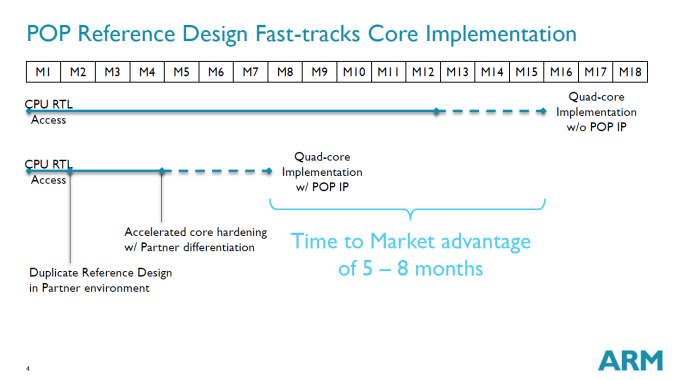

<p>The main goal is to relieve the vendor from re-doing work that ARM has already done and thus enable a much better time-to-market compared to vendors which have their in-house implementation methodology (Samsung and Qualcomm, among others, for example). ARM explains this can give an up to 5-8 month time to market advantage which is critical in the fast-moving mobile SoC space.</p>

<p>One aspect that seemed to be misunderstood, and even myself had some unclear notions about, is that POP IP is not a hard-macro offering but rather all the resources that enable a vendor to achieve that hard-macro (GDSII implementation).</p>

<p>This is where we come back to today's announcement. ARM's new POP IP targets UMC's new 28nm process called <span style="color: rgb(68, 68, 68); line-height: 21px;">28HPC</span><sup style="color: rgb(68, 68, 68); line-height: 21px;">U </sup><span style="color: rgb(68, 68, 68); line-height: 21px;">for ARM's Cortex A7 and Cortex A53 cores</span><span style="color: rgb(68, 68, 68); line-height: 21px;">. The acronym has a dual meaning standing for 28nm High Performance Compact "UMC" or "Ultra-Low I<sub>DDQ</sub>" with I</span><sub style="color: rgb(68, 68, 68); line-height: 21px;">DDQ </sub><span style="color: rgb(68, 68, 68); line-height: 21px;">being the leakage current which is being describes as being considerably lower than UMC's first-generation 28nm HKMG process and able to give significant battery life improvements to devices. </span></p>

<p><span style="color: rgb(68, 68, 68); line-height: 21px;">While ARM isn't able to disclose which vendors use POP IP, they state that the main target is low-cost Asian market, which most likely means various Chinese vendors. According to</span> S.C. Chien, vice president, corporate marketing, UMC:</p>

<p style="margin-left: 40px;"><em>"Multiple customers from a variety of applications have engaged with UMC to design their products on 28HPC<sup>U</sup>. Our collaboration with long-time partner ARM enables UMC to offer a comprehensive design platform with POP IP for two of the most efficient ARM processor cores."</em></p>

</p><p align="center"><img src='http://dynamic1.anandtech.com/www/delivery/avw.php?zoneid=24&cb=951110506&n=a1f2f01f' border='0' alt='' /> </p> </p>

Read more...

Source: AnandTech

This channel features the latest computer hardware related articles. |

|